## **User's Manual**

## Model XLMXXV Universal Logic Module For VME Systems

JTEC Instruments 32 Thompson Rd. Rochester, NY, USA Tel: (585)-334-7215 http://www.jtec-instruments.com

Information furnished by JTEC Instruments (JTEC) is believed to be accurate and reliable. However, no responsibility is assumed by JTEC for its use, nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patents rights of JTEC. JTEC reserves the right to change specifications at any time without notice.

Copyright 2004 by JTEC

Manual #: mdo-XLMXXV-MAN-001.1 September 2004

#### TABLE OF CONTENTS

| 1. | OV       | ERVIEW                                      |     |

|----|----------|---------------------------------------------|-----|

| 1  | .1.      | SUMMARY OF FEATURES                         | . 3 |

| 1  | .2.      | POSSIBLE APPLICATIONS                       |     |

| 2. | SPE      | CIFICATIONS                                 | . 4 |

| 3. | AR       | CHITECTURE                                  | . 6 |

| 3  | .1.      | DEVICES                                     |     |

| -  | 3.1.     |                                             |     |

|    | 3.1.     |                                             |     |

|    | 3.1.     |                                             |     |

|    | 3.1.4    |                                             |     |

|    | 3.1.     |                                             |     |

|    | 3.1.     |                                             |     |

|    |          |                                             |     |

| 2  | 3.1.     |                                             |     |

| 3  |          | BUSES                                       |     |

|    | 3.2.     |                                             |     |

|    | 3.2.     |                                             |     |

|    | 3.2.     |                                             |     |

|    | 3.2.4    |                                             |     |

|    | 3.2.     |                                             |     |

|    | 3.2.     |                                             |     |

| 3  | .3.      | VMEBus ADDRESS SPACE                        | 10  |

| 4. | OPE      | ERATING INSTRUCTIONS                        | 11  |

| 4  | .1.      | HARDWARE SETUP                              | 11  |

|    | 4.1.     | 1. IMPORTANT WARNINGS                       | 11  |

|    | 4.1.2    |                                             |     |

|    | 4.1.     |                                             |     |

| 4  | .2.      |                                             |     |

|    | 4.2.     |                                             |     |

|    | 4.2.     |                                             |     |

|    | 4.2.     |                                             |     |

| 1  | ч.2<br>З |                                             |     |

| -  | 4.3.     |                                             |     |

|    | 4.3      |                                             |     |

|    |          |                                             |     |

|    | 4.3.     |                                             |     |

|    | 4.3.4    |                                             |     |

| 4  |          | PROGRAMMING OF THE USER FPGA                |     |

|    | 4.4.     |                                             |     |

|    | 4.4.     |                                             |     |

|    | 4.4.     |                                             |     |

|    | 4.4.4    |                                             | -   |

|    | 4.4.     | 5. CONFIGURING FPGA                         | 28  |

| 4  | .5.      |                                             |     |

|    | 4.5.     |                                             |     |

|    | 4.5.     | 2. USER'S GUIDE TO HOST-PROCESSOR INTERFACE | 30  |

|    | 4.5.     | 3. THE DSP BOOT PROCESS                     | 32  |

| 4  | .6.      | The INTERRUPT SYSTEM OF XLMXXV              | 33  |

|    | 4.6.     |                                             |     |

|    | 4.6.     |                                             |     |

|    | 4.6.     |                                             |     |

|    | 4.6.4    |                                             |     |

|    | 4.6.     |                                             |     |

|    | 4.6.     |                                             |     |

| Л  | 4.0.0    | OPERATIONS ON THE FLASH MEMORY              |     |

| 4  | • • •    |                                             |     |

|    | 4.7.     | 1. FPGA UTILITY CONFIGURATION               | 20  |

| 5. APPENDICES                                  |  |

|------------------------------------------------|--|

| 5.1. USER CONSTRAINTS FILE, UCF                |  |

| 5.2. USING UTILITY CONFIGURATION OF FPGA       |  |

| 5.2.1. WRITING TO THE IRQ MAILBOX OF INTERFACE |  |

| 5.2.2. TEST DATA PATTERNS                      |  |

## JTEC Model XLMXXV Universal Logic Module

## **1. OVERVIEW**

JTEC Model XLMXXV is a highly versatile, general-purpose, programmable universal logic module for use in VME-based systems. The desired logic operations are performed by a Xilinx Virtex series Field Programmable Gate Array (FPGA), while more elaborate numeric operations are performed by a Texas Instruments 900-Mflops/s floating-point Digital Signal Processor (DSP) TMS320C6711. XLMXXV is a derivative of XLM72V, with most of ECL-TTL translators and I/O headers being replaced by a 120-pin mezzanine connector. It is, thus, intended for use with custom mezzanine boards offering a high degree of flexibility in I/O electric standards, including analog I/Os.

On the other end, XLMXXV communicates with computers via the VMEBus, utilizing 32-bit addressing and 32-bit and 16-bit data transfer, including 32-bit block transfer at rates of up to 40 Mbytes/s. Further, XLMXXV features two banks of fast asynchronous static random access memory (ASRAM), 2 Mbytes each, accessible to VMEBus, FPGA, and DSP, and it features an on-board 2 Mbyte EEPROM or flash memory allowing one to store up four FPGA configuration files.

Few digital applications are out of XLMXXV range.

## **1.1. SUMMARY OF FEATURES**

- One 120-pin and one 60-pin mezzanine connector, accepting mezzanine I/O boards.

- Optional 16 front-panel ECL ports, substituting the 60-pin mezzanine connector, configurable in quartets as either inputs or, with some exceptions, as outputs, organized in one 34-pin and one 8-pin headers. Three ports can be configured as external clock ports supporting rates of up to 110 MHz. The clock ports are inputs only.

- One user-programmable FPGA, XCV(50-300)-PQ240 by Xilinx, Inc.

- One user-programmable, floating point DSP, TMS320C6711 by Texas instruments, rated at 900 Mflops/s.

- 2 banks of fast asynchronous SRAM, 2 Mbytes each, addressable in 32-bit, 16-bit and 8-bit words.

- A custom, programmable, in-system reconfigurable VMEBus interface and bus router/arbitrator.

- One 4-Mbyte programmable erasable read-only memory holding up to two FPGA configuration files.

- Four front-panel LEDs, one indicating VMEBus operation and the remaining three being user-programmable, mapped onto ports of the user FPGA.

## **1.2. POSSIBLE APPLICATIONS**

- Wave-form digitizer, when used in conjunction with an optional mezzanine board

- Intelligent Data Buffer

- Scalers, Prescalers, Coincidence Registers, Time Stampers

- Multilevel Trigger Logics

- Digital Delay and Gate Generators

- Detector Readout Processor

- Histogramming Memory

Due to the ultimate parallelism of an FPGA, XLMXXV can be programmed to perform multiple functions simultaneously, whether related or completely unrelated. For example, part of XLMXXV may be programmed to function as a wave-form digitizer, while other parts execute trigger logic, yet another parts serving as a block of gated and non-gated scalers, and yet another part serving as digital delay and gate generators.

## **2. SPECIFICATIONS**

Formfactor: 6U VME.

PC Board: 8-layer, double-sided mixed surface-mount and through-hole.

VME Connectors: 96-pin J1, J2, and 30-pin JAUX implementing CERN extensions.

Optional ECL Ports: 16, mapped onto the user FPGA.

Mezzanine Connectors: one 120-pin and one 60-pin, the latter replacing the optional ECL ports

- **LEDs:** one to indicate VMEBus operations, three user-programmable, via the FPGA configuration.

- Clocks: one 80 MHz shared by the VMEBus interface and FPGA; one 37.5 MHz for DSP.

External Clock Inputs: up to three, rated at 110 MHz.

**FPGA:** Virtex series XCV(50-300) by Xilinx.

- **DSP:** TMS320C6711 by Texas Instruments.

- ASRAMs: 16 CY7C1024B-15CV, organized in two banks of 2-Mbyte 32-bit memory.

- FPGA Configuration Memory: 4-Mbyte AT29C040A by Atmel.

- VMEBus Addressing: 32-bit, geographic.

- VMEBus Data Transfer: 32-bit and 16-bit; 32-bit block transfer at rates of up to 40 Mbytes/s.

- Front Panel: Black, anodized, with white silk-screen labeling; two ejector handles with anodized blue ID plates.

- **Power Requirements:** +5V at approximately 1.5 A; -5.2V at approximately 600 mA; -2V at approximately 100 mA. Depends on ECL port usage.

## **3. ARCHITECTURE**

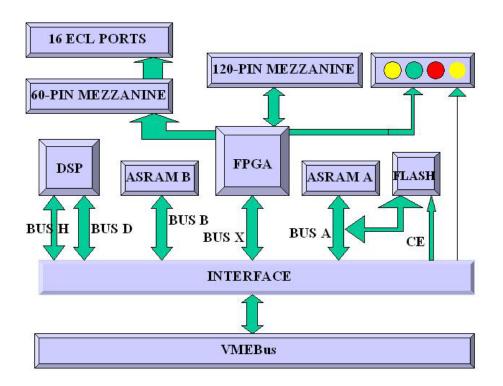

XLMXXV features a number of distinct devices, interconnected by address, data, and control buses in star-like topology. Two devices, the FPGA and the DSP may serve, along with the VMEBus, as bus masters, assuming and releasing control of the buses according to user-programmable routines. A block-diagram of XLMXXV is illustrated in Fig. 1.

Fig. 1. Block-diagram of XLMXXV.

Interaction of devices and routing of buses is discussed in Sections 3.1 and 3.2, further below.

## **3.1. DEVICES**

XLMXXV features eight distinct devices, five of which are addressable via VMEBus. The addressable devices include:

(i, ii) two banks of fast asynchronous static random access memories (ASRAM),

(iii) one Field-Programmable Gate Array (FPGA),

(iv) one floating-point digital signal processor (DSP) (more accurately, the host processor interface, HPI, of this processor), and

(v) a VMEbus Interface and Bus Arbiter/Router Array (Interface).

The non-addressable (by VMEBus) devices are accessible to the user FPGA and include:

- (vi) one flash memory to store configuration data for the FPGA,

- (vii) an array of 72 ECL ports, and

- (viii) an array of four front-panel diagnostic light-emitting diodes.

#### 3.1.1. ASYNCHRONOUS STATIC RANDOM ACCESS MEMORY

XLMXXV features two banks of fast asynchronous static random access memory, referred to as ASRAM A and ASRAM B. Both banks are identical and consist of four CY7C1024B-15VC ICs manufactured by Cypress Semiconductor, Inc., providing for 2 Mbytes of storage capacity, each. They are configured as 32-bit wide memory, but can be also accessed in half-words by both, VMEBus and by the DSP, and by half-words and byte-wise by the FPGA.

#### 3.1.2. FIELD PROGRAMMABLE GATE ARRAY

The desired logical operations of XLMXXV are to be programmed by the user into a Xilinx XCV(50-300)-PQ240C field programmable gate array chip (FPGA). Any logic that can be implemented as synchronous state machine or combinatorial equation may be programmed, subject only to the availability of resources of the Virtex series XCV\* chip, which are quite vast. For an XCV300, these resources include, among other things:

- (i) 6912 logic cells,

- (ii) 322,970 system gates,

- (iii) 1536 complex logic blocks,

- (iv) 65,536 block RAM bits, and

- (v) Built-in clock-management circuitry with four DLLs.

The FPGA is clocked at 80 MHz from an on-board clock, but can be also clocked externally via one of four special ECL ports at rates of up to 110 MHz. The FPGA features DLLs, which can be used to double the internal clock rate.

The FPGA can access Interface registers, and both banks of ASRAM. Further, it has exclusive control of Flash Memory, of all ECL ports, and of three out of four front-panel diagnostic LEDs.

#### 3.1.3. DIGITAL SIGNAL PROCESSOR

To allow one to perform more complex numerical operations on data that are beyond the capabilities of the user FPGA, XLMXXV is equipped with a Texas Instruments TMS320C6711 floating-point digital signal processor. The processor is clocked at 150

MHz and, given its 6 parallel processors, is rated at 900 Mflop/s. The DSP can access select registers of the Interface and both banks of ASRAM, in either 32-bit data words or in 16-bit words. VMEBus can access the DSP via the Host Port Interface (HPI) of the latter.

#### 3.1.4. VMEBUS INTERFACE AND BUS ROUTER/ARBITER

The communication between VMEBus and various devices of XLMXXV is mediated by an interface and bus router/arbiter array implemented in four Xilinx Complex Programmable Logic Devices (Interface). The Interface is comprised of one XC95216-10PQ160C and three XC95288XL-7TQ144C chips. Individual CPLDs can be reprogrammed in-system via the on-board JTAG port, allowing one to alter the functionality of the Interface should a need arise. The Interface serves also as a multiplemaster bus router and arbiter, such that it may route in parallel bus needs by more than one master. Since XLMXXV features three masters, VMEBus, FPGA, and DSP, there is a need not only for bus routing but also for bus arbitration. The needed arbitration scheme is also implemented in the Interface array.

Furthermore, some of the registers of the Interface serve the role of mailboxes for sending messages between the VMEBus, DSP, and the FPGA. In particular, such registers are used to implement interrupt and polling schemes required by various data acquisition systems.

#### 3.1.5. FLASH MEMORY

To provide for the storage of the FPGA configuration data, XLMXXV is equipped with one 4 MBit Programmable Erasable Read-Only Memory (Flash Memory), an ATMEL AT29C040A. The size of this memory is sufficient to accommodate up to two configuration files, one of which is a default boot configuration. The Flash Memory is socketed, but can be reprogrammed in system. The chip is rated for 10,000 programming cycles and 20-year data retention.

#### 3.1.6. ECL PORTS

XLMXXV is equipped with 72 ECL ports organized in four 34-pin and one 8-pin header. The ports are controlled exclusively by the FPGA and can be configured in quartets as either inputs or outputs, but always unidirectional. Four ECL ports serve special role, as they are associated with clock inputs of the FPGA. As such they can serve as inputs for external clock signals to the FPGA.

#### 3.1.7. DIAGNOSTIC LEDs

XLMXXV is equipped with four front-panel light-emitting diodes (LED), one of which (yellow) signals VMEBus operations by the Interface and the remaining three (red, green, and yellow) being controlled by the FPGA and, hence, by the user configuration. Every

LED is driven via a pulse-length extender such that even short, 20ns-long pulses produce robust flashes, while long pulses or DC levels are transmitted to the LED unaltered.

### **3.2. BUSES**

Devices of XLMXXV and the VMEBus communicate with each other via the VMEBus and five internal buses. All communications are mediated by the Interface, which routes addresses and data generated by the three masters, VMEBus, FPGA, and DSP, to the respective target devices. The Interface allows for a concurrent access of several buses by several masters and performs at the same time the function of the bus arbitrator.

#### 3.2.1. INTERFACE-TO-ASRAM BUSES

The two ASRAMs, ASRAM A and ASRAM B, communicate with the Interface via their respective buses, named Bus A and Bus B, respectively. Each of these buses has 19 address, 32 data, and 3 control lines. Bus A is shared with the Flash Memory, with the exception of one control line, for which the Flash Memory has its individual counterpart.

Buses A and B can be controlled, by any of the three masters, VMEBus, FPGA, and DSP. Which, in practical terms, means that any one of these three masters can write to or read from either of the two banks of ASRAMs.

#### 3.2.2. INTERFACE-TO-FPGA BUS

The FPGA communicates with the Interface via a bus named Bus X, featuring 19 address, 32 data, and 26 control lines. Bus X can be controlled by either the VMEBus or the FPGA.

#### 3.2.3. INTERFACE-TO-DSP BUS

The DSP communicates with the Interface via a bus named Bus D, featuring 19 address, 32 data, and 11 control lines. Bus D is controlled exclusively by the DSP.

#### 3.2.4. INTERFACE-TO-HPI BUS

The Host Processor Interface (HPI) of the DSP communicates with the Interface via a bus named Bus H, featuring 16 data and 7 control lines. Bus H is controlled exclusively by the VMEBus.

#### 3.2.5. BUS ARBITRATION SCHEME

Buses A, B, and X can be controlled by more than one master and, consequently, an arbitration scheme is provided by the Interface to guarantee each of the three masters, the

VMEBus, FPGA, and DSP access to these buses, while avoiding bus contention. The arbitration scheme is based on the "first-come-first-serve-release-when-done" principle, whereby the masters are granted control of buses on first-come-first-serve principle and are required to release the control upon completion of their task.

Masters post their bus requests in the respective bus request registers of the Interface. The requests are placed on the queues associated with individual buses and are granted as soon as the bus involved becomes available. The grant of the bus control is signaled to the requesting master by the content of the respective bus grant register. The requesting master, upon detection of the bus grant signal, takes control of the bus, performs the intended task, and removes its request from the request register, making the bus available to the master that is first in the queue.

#### 3.2.6. INHIBIT OF BUS ACCESS BY FPGA AND DSP

The Interface provides the VMEBus with the capability to inhibit the control of buses by the remaining two masters, the FPGA and the DSP. In other words, the VMEBus can, at will, "snatch" the bus control already in progress from the FPGA and/or DSP, so as to allow it to perform urgent or emergency tasks of its own. The response of the FPGA and the DSP to the bus "snatching" is at the discretion of the user and is to be programmed into the FPGA and the DSP, respectively. A reasonable programming is assumed to detect the occurrence of "snatching" and provide for its smooth handling, e.g., the abortion of the current operation and release of the request or, when feasible, suspension of the current operation and its resumption upon removal of the bus grant inhibit.

## **3.3. VMEBus ADDRESS SPACE**

The address spaces of the five addressable devices of XLMXXV are defined by 24 bits, A0 - A23 of the complete VMEbus address, bits A24 - A26 being disregarded and bits A27 - A31 carrying the geographical address of XLMXXV.

| ASRAM A   | 000000h - 1FFFFCh                                   |

|-----------|-----------------------------------------------------|

| ASRAM B   | 200000h - 3FFFFCh                                   |

| FPGA      | 400000h - 5FFFFCh, used freely at user's discretion |

| DSP/HPI   | 600000h - 7FFFFCh, most of which is unused          |

| INTERFACE | 800000h – 9FFFFCh, most of which is unused          |

## 4. OPERATING INSTRUCTIONS

Successful operation of XLMXXV requires its proper hardware setup, the programming of its user FPGA and/or DSP, and the computer-access of its five addressable devices via VMEBus.

## 4.1. HARDWARE SETUP

The hardware setup of XLMXXV includes (i) configuring its front-panel ECL ports for operation in conjunction with the intended FPGA configuration and (ii) making sure that the three blocks of jumpers, JP34 – JP36 are configured properly. Furthermore, one is expected to connect respective ECL ports to external devices with twisted-pair or flat ribbon cables. The ECL ports are configurable in quartets either as inputs or outputs. The four ports identified by silk-screen labels (on the front panel and on the XLMXXV board) as E1-E4 play a special role as they connect via ECL-to-TTL translators (MC10125) to primary (PGCK) clock inputs (E1-E3) and secondary (SGCK) inputs (E4) of FPGA. These FPGA inputs can be used to drive intrinsic clock nets of FPGA. Accordingly, ports E1-E4 can and should be used to supply external clock signals, up to 110 MHz, to XLMXXV.

#### 4.1.1. IMPORTANT WARNINGS

Improper configuration of ECL ports may lead to the damage of translator ICs or a costly damage of the XLMXXV board or of the user FPGA. A special care should be taken to correctly identify and populate the sockets with translator ICs. When not sure, please consult JTEC Support service.

Warning 1: Only one translator IC (either input or output) is allowed for any single port. Which, in practical terms, means that in any horizontal pair of sockets at most one should be filled.

Warning 2: When configuring input ports (MC10125), it must be ascertained that the corresponding ports of the FPGA are configured, indeed, as input ports and not as output ports. In particular, this applies to the default "boot" configuration of the FPGA active upon power-up.

To avoid ports conflict right upon power-up, it is recommended to keep as the default "boot" configuration the general Utility Configuration supplied originally with XLMXXV, or its possible update. This Utility Configuration has no FPGA ports configured as outputs and, hence, guarantees that there is no conflict with any translator IC.

Warning 3: XLMXXV requires differential ECL inputs and will not function properly (no damage will occur, though) with single-ended ECL signals. Which means, among other things, that these inputs cannot be driven by an ECL bus connected to ECL outputs of multiple external devices.

Warning 4: When configuring output ports, make sure that the input-polarizing resistor arrays for the particular quartets of ECL ports, are removed from their respective sockets.

#### 4.1.2. CONFIGURING ECL PORTS

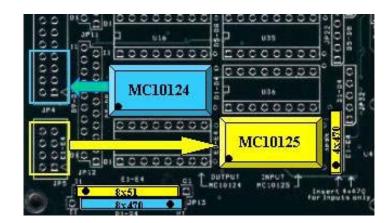

ECL-to-TTL conversion (input) and TTL-to-ECL conversion (output) is accomplished by 16-pin MC10125 and MC10124 ICs, respectively. Each converter IC is capable of interfacing up to four differential ECL ports to respective four TTL ports of the user FPGA. Differential inputs of these ICs are directly connected to respective pairs of pins of front-panel headers. The headers are identified (going from top to bottom) by labels A, B, C, D, and E, respectively while individual ports within a header are identified by numbers 1 through 17 (ports A – D) or 1 through 4 (port E). It is important to note that (as indicated on the front panel of XLMXXV) port 1 of each of the five headers is represented by the bottom pair of pins of the header and, thus, for example, ports A1-A4 are the four bottom pairs of pins of the top-most 34-pin header.

As indicated by silk-screen labels printed right below each of the two columns of 18 16pin sockets, the input translators are to be placed into sockets in the right-most column while the output translators are to be inserted into sockets of in the left-most column. The correspondence between the sockets and the ECL ports is indicated by silk-screen labels printed between the two columns of 16-pin sockets. Note that 17-th ports (top-most) of headers A – D are associated with the pair of sockets labeled A17-D17 – 9-th pair from top.

In addition to translator ICs, proper functioning of ECL ports requires either impedancematching resistor arrays of 8 x 50 $\Omega$  (input ports) or pull-down resistor arrays of 8 x 470 $\Omega$ (output ports). These two types of arrays share "Zig-Zag" sockets, with the exception of their first (common) pins, marked by dots. The correspondence between the ECL ports and the (10-position) rows of the "Zig-Zag" sockets is indicated by silk-screen labels printed on both sides of these sockets.

Figure 2 illustrates placement of translator chips and resistor arrays for ECL ports D1-D4 configured as output ports and ports E1-E4 as input ports. Dots indicate pins #1.

Fig. 2. Placement of ECL port components for inputs (yellow) and outputs (blue).

#### 4.1.2.1. CONFIGURING IMPEDANCE-MATCHING RESISTOR ARRAYS FOR ECL INPUT PORTS

As noted in subsection 4.1.2 further above, to avoid reflections of incoming signals from the ECL input ports, 8 x 50 $\Omega$ resistor arrays are to be inserted into proper rows of the "Zig-Zag" sockets. Note that each (differential) ECL input is associated with two signal lines and that both these lines need to be terminated. Which is why for one quartet of inputs eight terminating resistors are needed. The 8 x 50 $\Omega$  arrays are to be inserted with their common pins entering sockets marked as I1 (top-most sockets in the case of the 7 vertical Zig-Zag sockets and left-most sockets in the case of the 2 horizontal Zig-Zag sockets).

Warning: Even though each row of a 20-pin Zig-Zag socket is capable of accommodating a typical commercial 9 x 50 $\Omega$  resistor array with ten pins, one should use only 8 x 50 $\Omega$  arrays. This is so, because the pins on the opposite end (with respect to 11) of the Zig-Zag sockets, labeled as O1, are connected to -5.2V, to supply pull-down voltage for output port resistor arrays (8 x 470 $\Omega$ ) (see also subsection 4.1.2.3).

Note that general rules for bussing of ECL input ports require that only the last port on the bus has its terminating resistor installed.

#### 4.1.2.2. CONFIGURING INPUT POLARIZING RESISTORS

To guarantee a default logical zero at ECL input ports that are not externally driven, XLMXXV provides sockets for respective polarizing (pull-down of complementary ECL input line) resistor arrays. These sockets are located next to the input translator sockets and are associated directly with the adjacent socket. This association is also reflected in the silk-screen label printed next to the socket. Position of the pin 1 (common) is in this case indicated by the "cut corner" of the silk-screen socket outline (bottom). The input-

polarizing resistors should be removed when the particular ports are configured as output ports.

Note, that the use of polarizing resistors is not mandatory, unless the user configuration of FPGA relies on a definite polarization. It may be, however, a sound practice to use these resistors with every input translator.

Note that general rules for bussing of ECL input ports require that only the last port on the bus has its polarizing resistor installed.

#### 4.1.2.3. CONFIGURING OUTPUT PULL-DOWN RESISTORS

For a proper operation of ECL output ports, 8 x 470 $\Omega$  pull-down resistor arrays are to be inserted into proper rows of the "Zig-Zag" sockets. Note that each (differential) ECL output is associated with two signal lines and that both these lines need to be pulled down, via resistors, to V<sub>EE</sub>=-5.2V. Which is why for one quartet of outputs, eight pulldown resistors are needed. The 8 x 470 $\Omega$  arrays are to be inserted with their common pins entering sockets marked as O1 (bottom sockets in the case of the 7 vertical Zig-Zag sockets and right-most sockets in the case of the 2 horizontal Zig-Zag sockets).

Warning: Even though each row of a 20-pin Zig-Zag socket is capable of accommodating a typical commercial 9 x 470 $\Omega$  resistor array with ten pins, one should use only 8 x 470 $\Omega$  arrays. This is so, because the pins on the opposite end (with respect to O1) of the Zig-Zag sockets, labeled as I1, are connected to ECL bias voltage, to supply terminating voltage for input port resistor arrays (8 x 50 $\Omega$ ) (see also sub-section 4.1.2.1).

Note that general rules for bussing of ECL output ports require that only the last port on the bus has its pull-down resistor installed.

#### 4.1.3. JUMPER SETTINGS

There are three jumper blocks on the XLMXXV board that must be properly configured for a normal operation of the module. These are the 3-pin JP34 on the top of the board (front-panel facing left), the 6-pin JP35 close to the upper left corner of DSP (TMS320C6711), and the 3-pin JP36 right below JP35.

#### 4.1.3.1. JP34 SETTINGS – FPGA DEFAULT BOOT SOURCE

JP34 has two positions identified by silk-screen labels "SPROM" and "JTAG", respectively. For normal operation, the jumper should be placed in the "SPROM" position, i.e., connecting the two left-most pins of JP34. This allows FPGA to boot upon power-up from the default "boot" sector of the flash memory (socketed AT29C040A to the left of JP34). The "JTAG" position of JP34 is intended primarily for in-system-programming/reprogramming, in conjunction with the 6-pin JP33 JTAG header, of the four complex programmable logical devices (CPLDs) constituting the Interface. Since the

user FPGA is in a common JTAG chain with the Interface CPLDs, it can be programmed via the JTAG port too, when JP34 is set to "JTAG".

#### 4.1.3.2. JP35 SETTINGS – DSP BOOT SOURCE AND DATA SIZE

JP35 is used to select the boot source and the size of the boot data for DSP. It has three pairs of pins, with one pair serving only as a storage bin. The significance of various jumper settings is described by the silk-screen label located right to JP35. It is shown in Table 1 below

1-23-4Boot Source/DataWord SizeOFFOFFASRAM A/8-bitsONOFFASRAM A/32-bitsOFFONHPI/16-bit (Default)ONONASRAM A/16-bits

Table 1. Settings of DSP boot mode jumpers.

#### 4.1.3.3. SETTINGS OF JP36 – DSP ENDIANNESS

JP36 selects endianness of DSP, as indicated by the silk-screen labels to its right. With a jumper in the lower position "LE", DSP operates in little-endian, while with a jumper in the upper position "BE", DSP operates in big-endian.

# 4.2. ADDRESSING AND DATA FORMATTING CONVENTIONS

Further below, the role of individual bits in various address and data words will be discussed, as well as the significance of various addresses and values of data words stored at these address locations. The rules adopted to identify individual bits and to interpret address and data words are presented in sub-sections 4.2.1. - 4.2.3, below.

#### 4.2.1. BIT NUMBERING IN ADDRESS AND DATA WORDS

Whenever the role of individual bits, either in address or data words is discussed, it will be assumed further below that the least significant bit has index zero. Accordingly, the most significant bit in a 32-bit word is bit 31.

#### 4.2.2. ADDRESS REPRESENTATION

XLMXXV allows only 32-bit addressing, with the five most significant bits of this address representing the slot number occupied by XLMXXV or, in other words, its

geographic address. To address the total of five addressable internal devices, XLMXXV implements a 24-bit scheme, where the 3 most significant bits identify the device of interest and the remaining 21 bits identify the internal register or memory location of the device. Note that 21 bits are needed to make use of the full capacity of individual ASRAM banks. Therefore, further below, for the sake of simplicity, all addresses are expressed in the form of 5-digit hexadecimal numbers, with a tacit understanding that a full VMEBus address has always bits 24 through 26 set to zero and that bits 27 through 31 encode geographic address.

#### 4.2.3. ENDIANNESS

Endian is a term commonly used to describe the way multi-byte data words are stored in memory. VMEBus is inherently big-endian, such that bytes of increasing hierarchy are stored at memory locations of decreasing addresses. Which means that the most significant byte of a multi-byte word is stored at lowest memory location and the least significant byte at highest memory location. Accordingly, data bytes of highest significance are transferred over VMEBus data lines of lower indices. And so, in 32 bit transfers, the most significant byte is transferred over data lines D0-D7, the second most significant byte, over data lines D8-D15, the second least significant byte, over data line D16-D24, and the least significant byte is transferred over data lines D25-D31. Similarly, in 16-bit transfers, the most significant byte is transferred over data lines D0-D7 and the least significant byte, over data lines D8-D15.

On the other hand, modern PC's are mostly little-endian, such that higher hierarchy bytes occupy higher memory locations. Also, modern VME crate controllers often offer the capability of a fast hardware conversion between the big- and little-endian formats. With this in mind, the present manual uses little-endian format, i.e., all data discussed further below are represented in little endian format.

### 4.3. SOFTWARE ACCESS OF INTERNAL DEVICES

#### 4.3.1. ACCESSING INTERFACE REGISTERS

The use of the memory space of the Interface is fixed by the Interface firmware at the design or upgrade time. The VMEbus must write to proper locations of this space to accomplish the following tasks:

- (i) Request control of any of the three, shared internal buses that are subject to bus arbitration, Bus A, Bus B, and Bus X (see also Section 3.2).

- (ii) Issue interrupt signals to the DSP and FPGA and toggle reset lines for these devices.

- (iii) Write the interrupt request ID to the proper IRQ mailbox.

- (iv) Select the "warm" boot source for the FPGA, which is either one of the 4 banks of the Flash Memory, or ASRAM A (See also Section X).

- (v) Snatch the bus control from the FPGA and the DSP.

- (vi) Reset the FPGA and DSP Interrupt Service Registers and Flags.

The VMEbus must read from proper locations of the address space to accomplish the following tasks:

- (i) Check if the requested control of any of the buses has been, indeed, granted.

- (ii) Check what the actual FPGA boot source is.

- (iii) Check the actual ownership of the three arbitrated buses.

- (iv) Poll the Interrupt Service Registers of the FPGA and DSP for the presence of service requests.

Addressing of the Interface registers may appear somewhat peculiar, due to the fact that the Interface is implemented in four Complex Programmable Logical Devices (CPLDs), each of which has access only to a portion (non-contiguous) of the VMEBbus address bus. For example, the "Master" CPLD controlling the Interface logics has access only to the VMEbus data lines D0, D1, D16, and D17, as well as to the address lines A1, A2, A3, A16, and A17. Which is why, with few exceptions, accessing of the Interface is accomplished over the data lines D0, D1, D16, and D17 and address lines A2, A3, A16, and A17, accounting for the apparent peculiarity of the Interface addressing and data scheme.

Addresses of the Interface registers are shown in Table 2 below. Note that bit 23 is always set to "1", to select the Interface as the target device. Note also that to form a complete VMEbus address, the 24-bit addresses shown in Table 2, must be pre-pended by a 5-bit geographical address, followed by three "don't" care bits.

| Address bits | Registers accessed or action induced                      |

|--------------|-----------------------------------------------------------|

| A0-A23       |                                                           |

| 800000h      | Bus control register and IRQ flags (write/read)           |

| 800004h      | FPGA and DSP reset register (write-only)                  |

| 800008h      | FPGA boot source register (write/read)                    |

| 80000Ch      | Inhibit flag for the bus control by FPGA and DSP          |

| 810000h      | Bus A ownership register (read-only)                      |

| 810004h      | Bus B ownership register (read-only)                      |

| 810008h      | Bus X ownership register (read-only)                      |

| 820000h      | Clear IRQ Mailboxes and the associated flags (write-only) |

| 820004h      | Interrupt FPGA (write-only)                               |

| 820048h      | Serial number (read-only)                                 |

| 820824h      | Mailbox register (read-only)                              |

| 821048h      | DSP mailbox and interrupt (write-only)                    |

Table 2. Use of the Interface address space.

The significance of data written to or read from the valid locations of the Interface address space is discussed in detail in sub-sections 4.3.1.1-4.3.1.9 below.

#### 4.3.1.1. BUS CONTROL REQUEST REGISTER AT 800000h

The bus control register located at 800000h is a 3-bit register mapped onto bits 0, 1, and 16 of the 32-bit VMEBus word. When set by a "Write" operation, they indicate to the bus arbitrator the request by the VMEBus of the control of an arbitrated bus:

| Request Bus A         | REQA = 00000001h |

|-----------------------|------------------|

| Request Bus B         | REQB = 0000002h  |

| Request Bus X         | REQX = 00010000h |

| Request Bus B for DSP | REQD = 00020000h |

To release a bus, its respective request bit must be set to 0. Note that the Interface will always simultaneously set and/or release requests of all three buses, depending on which of the four bits, 0,1, 16, and 17 are set and which are reset.

Example: a combined request of all three buses of XLMXXV is achieved by writing (REQA OR REQB OR REQX) = 00010003 to the address 800000. To release all these three buses at the same time, one simply writes 0 to the same address.

#### 4.3.1.2. FPGA AND DSP RESET REGISTER AT 800004h

The FPGA and DSP reset register at 800004h is a 2-bit write-only register mapping onto bits 0 and 1 of the 32-bit VMEBus word. Depending on what data are written into these two bits, the Interface will set or release the reset signal of the FPGA or DSP. The action is always simultaneous on both register bits involved.:

| Set Reset for the FPGA | RESFPGA | = | 0000001h |

|------------------------|---------|---|----------|

| Set Reset for the DSP  | RESDSP  | = | 0000002h |

Reset signals are released by setting the associated bits to 0.

Example:

To only set the Reset for the FPGA, one must write (RESFPGA OR RESDSP OR IRQFPGA OR IRQDSP) = 1 to the memory location 800004. To release this reset one writes 0 to this memory location. Note that the latter causes then the FPGA to boot from the selected boot source.

#### 4.3.1.3. FPGA BOOT SOURCE SELECTOR REGISTER AT 800008

The FPGA boot source selector register is a write/read 4-bit register mapping onto bits 0, 1, 16, and 17 of the 32-bit VMEBus word:

| Select sector 0 of flash memory | BOOT0 | = 00000000h |

|---------------------------------|-------|-------------|

| Select sector 1 of flash memory | BOOT1 | = 0000001h  |

| Select sector 2 of flash memory | BOOT2 | = 0000002h  |

| Select sector 3 of flash memory | BOOT3 | = 0000003h  |

| Select ASRAM A                  | BOOTA | = 00010000h |

The BOOTA bit overrides the other BOOT bits that might be set.

Example:

To select ASRAM A as a boot source of the FPGA, one must write BOOTA=00010000h to the memory location 800008.

## 4.3.1.4. BUS CONTROL INHIBIT FLAG FOR FPGA AND DSP AT 80000Ch

Writing "1" to 80000Ch inhibits bus control by the FPGA and DSP, and makes all buses A, B, and X unconditionally available to the VMEBus. To actually gain the control of the desired bus, VMEBus must still request control of the bus. Writing "0" to 80000Ch removes inhibit and allows the FPGA and DSP to compete for the bus control.

## 4.3.1.5. BUS OWNERSHIP REGISTERS AT 810000h, 810004h, AND 810008h

Bus ownership registers at 810000h, 810004h, and 810008h are 2-bit read-only registers storing data identifying the actual owner of Bus A, B, and X respectively. The returned values of 0, 1, 2, and 3 indicate free status, and control by the VMEBus, FPGA, and DSP, respectively.

#### 4.3.1.6. XLMXXV SERIAL NUMBER REGISTER AT 820048h

The serial number register at 820048h is an 11-bit read-only register storing the XLMXXV serial number. This number is returned in bits 0 - 10 of the 32-bit data word.

## 4.3.1.7. INTERRUPT SYSTEM REGISTERS AT 820000h, 820004h, 820824h, AND 821048h

The significance and use of Interface addresses 820000h, 820004h, 820824h, and 821048h is discussed in detail in subsection 4.6.

#### 4.3.2. ACCESSING ASRAMs

One accesses either of the two ASRAMs by writing to or by reading from a desired memory location mapped onto the respective VMEBus address space of the ASRAM of

interest. As discussed in Section 3.3, the VMEBus address space for ASRAM A extends from 0h to 1FFFFCh and that of ASRAM B, from 200000h to 3FFFFCh.

The use of the address spaces of the two banks of ASRAMs is straightforward and involves writing of desired data into, or reading data from, the desired memory address. For example, writing data to the address 000008h causes this data to be stored in the memory location 8h of ASRAM A. As a second example, reading from memory location 200010h, will retrieve the content of the memory location 10h of ASRAM B.

#### 4.3.3. ACCESSING FPGA

The use of the address space of the FPGA remains at discretion of the user and is to be determined at the design time of the user FPGA code. One would expect here only a few low memory locations to be utilized with, perhaps, a suggestion to dedicate always the same location 0 for storing a read-only 32-bit ID of the particular user firmware.

#### 4.3.4. ACCESSING DSP

The DSP can be accessed via its Host Port Interface (HPI) over the dedicated BUS H. The use of this bus is described in detail in subsection 4.5.1.

## 4.4. PROGRAMMING OF THE USER FPGA

With Interface being an integral and tested part of XLMXXV, any further successful use of XLMXXV hinges critically on the quality of the user code loaded into the FPGA of XLMXXV. To write such a code, the user must know the role of all pins of the FPGA used in the design of XLMXXV and must know or establish safe timing patterns for interacting with other internal devices via write/read operations. The interaction mechanism of the FPGA with other Devices is described in detail below.

#### 4.4.1. *I/O PORTS*

As described in Section 4.1, XLMXXV features a total of 89 I/O ports presented at one 120-pin (73 ports) and one 60-pin (16 ports) mezzanine connector. The latter mezzanine connector can be replaced by 16 ECL ports.

For the actual numbers of the FPGA pins associated with pins of mezzanine connectors and/or with the optional 16 ECL ports see Tables 3 and 3a, below and also Appendix A. This appendix lists, with abundant comments, the relevant section of a user constraint file (\*.ucf) that can be used at the implementation time of the FPGA code. Note, that the user has no particular interest in knowing the pin associations, as the UCF file takes care of this task automatically, provided the design uses the proposed naming scheme.

| Mezz B | ECL  | FPGA  | Mezz. B | ECL  | FPGA  |

|--------|------|-------|---------|------|-------|

| Pin    | Port | Pad # | Pin     | Port | Pad # |

| 6      | A5   | 199   | 16      | A1   | 203   |

| 7      | A4   | 200   | 17      | A7   | 194   |

| 8      | A12  | 188   | 19      | A6   | 195   |

| 9      | B1   | 187   | 20      | A3   | 201   |

| 10     | A9   | 192   | 21      | A2   | 202   |

| 12     | A8   | 193   | 23      | B4   | 213   |

| 13     | A11  | 189   | 24      | В3   | 210   |

| 15     | A10  | 191   | 25      | B2   | 92    |

Table 3. Association between pins of the (60-pin) mezzanine connector B, optional ECL ports, and physical FPGA pad numbers.

Note, that FPGA pads 92, 210, and 213 are global clock pads and can, hence, be used only as inputs.

Table 3a. Association between pins of the (120-pin) mezzanine connector A and physical FPGA pad numbers.

| Mezz. A | FPGA  | Mezz. A | FPGA  | Mezz. A | FPGA  |

|---------|-------|---------|-------|---------|-------|

| Pin     | Pad # | Pin     | Pad # | Pin     | Pad # |

| 1       | 186   | 26      | 146   | 53      | 114   |

| 2       | 185   | 27      | 145   | 54      | 113   |

| 3       | 184   | 28      | 144   | 55      | 111   |

| 4       | 176   | 29      | 142   | 56      | 110   |

| 5       | 175   | 30      | 141   | 57      | 107   |

| 6       | 174   | 31      | 140   | 58      | 103   |

| 7       | 173   | 32      | 139   | 59      | 102   |

| 8       | 171   | 33      | 138   | 60      | 101   |

| 9       | 170   | 34      | 134   | 80      | 49    |

| 10      | 169   | 35      | 133   | 81      | 48    |

| 11      | 168   | 36      | 132   | 86      | 47    |

| 12      | 167   | 37      | 131   | 88      | 46    |

| 13      | 163   | 38      | 130   | 89      | 42    |

| 14      | 162   | 39      | 128   | 91      | 41    |

| 15      | 161   | 40      | 127   | 96      | 40    |

| 16      | 160   | 41      | 126   | 97      | 39    |

| 17      | 159   | 42      | 125   | 99      | 38    |

| 18      | 157   | 43      | 124   | 101     | 36    |

| 19      | 156   | 44      | 100   | 103     | 35    |

| 20      | 155   | 47      | 108   | 104     | 34    |

| 21      | 154   | 48      | 109   | 118     | 229   |

| 22      | 153   | 49      | 118   | 119     | 228   |

| 23      | 152   | 50      | 117   | 120     | 230   |

| 24 | 149 | 51 | 116 |  |

|----|-----|----|-----|--|

| 25 | 147 | 52 | 115 |  |

#### 4.4.2. LED PORTS

XLMXXV3 is equipped with three front-panel user-programmable LEDs, red, green, and yellow, controlled by FPGA configuration through expanding drivers. These drivers extend the duration of short pulses (of at least 2 clock cycle duration) to approx. 25 ms to provide for a robust flash of the associated LED, while not affecting the action of longer pulses. All LED ports are active high. A non-configured FPGA will cause all three LEDs to turn on - a state that can be taken as indicative of a failure of FPGA to boot. Conversely, user LEDs will signal a successful configuration of the FPGA by displaying a pattern foreseen by the user code.

In the UCF file (See Appendix 5.1) LED pads are named LEDOPD<1>-LEDOPD<3>, respectively. Their association with physical pads of the FPGA is shown in Table 4.

Table 4. Front-panel LED control pads of the FPGA

| LED | FPGA  | UCF Name of | LED   | FPGA  | UCF Name of | LED    | FPGA  | UCF Name of |

|-----|-------|-------------|-------|-------|-------------|--------|-------|-------------|

|     | Pad # | FPGA Pad    |       | Pad # | FPGA Pad    |        | Pad # | FPGA Pad    |

| Red | 99    | LEDOPD<1>   | Green | 97    | LEDOPD<2>   | Yellow | 96    | LEDOPD<3>   |

#### 4.4.3. DSP INTERRUPT PORTS

There are two lines connecting two pins of the FPGA to two interrupt pins of the DSP. One of them (NMIDX) is used by the FPGA to drive the non-maskable interrupt NMI of the DSP (pad C13 of the DSP), while the other one (INT6DX) drives the EXT\_INT6 pad D2 of the DSP. Both DSP interrupts are edge-driven by a low-to-high transition, with a requirement for the level to be low for at least two system clock cycles and then high for at least two cycles.

In the UCF file (see Appendix 5.1), the above two pins of the FPGA are labeled NMIDXOPD and INT6DXOPD, respectively. Their association with physical pins of the FPGA is shown in Table 5 below.

| Table 5. DSP I | nterrupt pads | of the FPGA |

|----------------|---------------|-------------|

|----------------|---------------|-------------|

| Interrupt | FPGA pin | Interrupt | FPGA pin |

|-----------|----------|-----------|----------|

| NMIDX     | 205      | INT6DX    | 206      |

#### 4.4.4. INTERFACE PORTS

With the exception of the two DSP interrupt signals discussed above, the FPGA communicates with all internal devices, as well as with the VMEbus, via the Interface, i.e., has direct connections only with pins of the constituent CPLDs of the Interface. These are 19 local address lines, labeled in the UCF as LOCADPD<2>-LOCADPD<20>, 32 local data lines, labeled in the UCF as LOCDAPD<0>-LOCDAPD<31>, and 20 control lines supplying signals necessary for executing various operations. The address and data signals, when accompanied by proper combination of control signals, propagate via Interface to address and data pins of a desired ASRAM or Flash Memory, while the Interface provides the output enable (OE) chip enable (CE), and write (WR) signals necessary for accessing any device. It is important to appreciate that the local address and data lines are bi-directional and, therefore, bi-directional pads and tri-state buffers must be used by the FPGA to connect to these lines. It is then up to the user to provide for proper enable signals for these buffers to achieve the desired result and, more importantly, not to cause a prolonged bus contention.

#### 4.4.4.1. BUS ARBITRATION PORTS

Since internal devices of XLMXXV can be accessed by up to three different masters, VMEbus, FPGA, and DSP, the presence of a reliable arbitration scheme is absolutely necessary. The user FPGA code must comply with the simple rules of bus arbitration not to cause prolonged bus contention that can lead to a destruction of components of XLMXXV. The arbitration scheme of XLMXXV is based on the first-come-first-serverelease-when-done principle. Therefore, every access of any internal device of XLMXXV by the FPGA (in fact, by any master) must be preceded by a request (issued to the Interface) for exclusive control over the needed bus(es) followed by a verification that such an access has been, indeed, granted. Naturally, grant of control over a bus to one master automatically denies control over this bus to any competing masters. At the conclusion of the access, the FPGA must remove the request, which releases the bus for subsequent arbitration. There are three bus request lines associated with the three internal buses subject to arbitration. These three buses are (i) Bus A, interconnecting Interface and ASRAM A, (ii) Bus B, interconnecting Interface and Bus B, and (ii) Bus X, interconnecting Interface and the FPGA. The bus interconnecting Interface and the DSP is owned exclusively by the DSP and is, hence, not subject to arbitration. The bus request signals are active low (so, a non-configured FPGA does not generate a false request). With each of the three bus request lines associated is a respective bus grant signal, active high. The bus grant signals are synchronized to the leading edge of the system clock. It is absolutely essential that the user configuration of the FPGA conditions enabling of local address lines of the FPGA by the presence of high on the Bus X grant line, as the Interface cannot here provide protection from a contention on bus X. Also, the user configuration must make sure that the local data buffers are not enabled when Interface is writing into the FPGA registers.

Since the control of the FPGA over bus A or over bus B always involves its control also over bus X, a request for bus X for the FPGA is generated automatically by the Interface itself whenever the FPGA requests either bus A or bus B.

In UCF (see Appendix 5.1), the bus A, B, and X request pads are labeled NREQAOPD, NREQBOPD, and NREQXOPD, respectively, while the associated grant pins are labeled ACKAIPD, ACKBIPD, and ACKXIPD. The association between the above arbitration signals and the FPGA pad numbers is shown in Table 6 below.

| Bus Request | FPGA pin | Bus Grant | FPGA pin |

|-------------|----------|-----------|----------|

| Α           | 56       | А         | 87       |

| В           | 64       | В         | 84       |

| Х           | 72       | Х         | 66       |

Table 6. Bus arbitration pins of the FPGA

#### 4.4.4.2. LOCAL ADDRESS PORTS

Local address lines are used to transmit address bits between the FPGA and the Interface, under assumption that these address bits will propagate via the Interface to the target device. The association between the local address bits and the FPGA pins is shown in Table 7 below.

| Table 7. Local | Address | pads of | f the | FPGA |  |

|----------------|---------|---------|-------|------|--|

|                |         |         |       |      |  |

| Address | FPGA  | Address | FPGA  | Address | FPGA  | Address | FPGA  |

|---------|-------|---------|-------|---------|-------|---------|-------|

| bit     | Pad # |

| 2       | 53    | 7       | 5     | 12      | 218   | 17      | 85    |

| 3       | 26    | 8       | 7     | 13      | 217   | 18      | 33    |

| 4       | 25    | 9       | 9     | 14      | 223   | 19      | 63    |

| 5       | 4     | 10      | 57    | 15      | 222   | 20      | 31    |

| 6       | 6     | 11      | 216   | 16      | 86    |         |       |

In UCF (see Appendix 5.1), local address pins are labeled LOCADPD<2>-<20>.

#### 4.4.4.3. LOCAL DATA PORTS

Local data lines are used to transmit data bits between the FPGA and the Interface, under assumption that these data bits will propagate via the Interface to the target device. The association between the local data lines and the FPGA pins is shown in Table 8 below.

| Data line | FPGA  |

|-----------|-------|-----------|-------|-----------|-------|-----------|-------|

|           | Pad # |           | Pad # |           | Pad # |           | Pad # |

| 0         | 68    | 8         | 232   | 16        | 71    | 24        | 3     |

| 1         | 74    | 9         | 11    | 17        | 80    | 25        | 10    |

| 2         | 18    | 10        | 21    | 18        | 24    | 26        | 23    |

| 3         | 27    | 11        | 236   | 19        | 28    | 27        | 237   |

| 4         | 50    | 12        | 208   | 20        | 20    | 28        | 207   |

| 5         | 13    | 13        | 235   | 21        | 17    | 29        | 215   |

| 6         | 234   | 14        | 224   | 22        | 238   | 30        | 209   |

| 7         | 12    | 15        | 220   | 23        | 231   | 31        | 221   |

#### Table 8. Local Data pads of the FPGA

In the UCF (see Appendix 5.1), local data pins are labeled LOCDAPD<0>-<31>.

#### 4.4.4.4. DATA BYTE ENABLE PORTS

While the data are addressed in XLMXXV in 32-bit words, there is a mechanism in place that allows one to access any arbitrary combination of bytes, without affecting the remaining bytes. One simply asserts a proper combination of data byte enable signals (active low), NDBEO<0>-NDBEO<3>. Note that since the index 0 refers to low data lines, it refers in fact to high data byte numbers (Big-Endian). For the most common and fastest 32-bit data transfer, all four NDBEO<0>-NDBEO<3> signals may be set permanently to 0, as they will be ultimately qualified within the Interface additionally by an appropriate device select signal to be generated by the FPGA. In the UCF (see Appendix 5.1), the data byte enable pins are labeled NDBEOPD<0>-NDBEOPD<3>. The correspondence between these signals and FPGA pins is shown in Table 9.

Table 9. Data Byte Enable pins

| Byte | FPGA pin |

|------|----------|------|----------|------|----------|------|----------|

| 0    | 82       | 1    | 67       | 2    | 73       | 3    | 95       |

#### 4.4.4.5. WRITE OPERATION PORTS

The FPGA signals to the Interface a write operation by asserting one or both of its NWRA and NWRB lines (active low). NWRA low indicates that the operation upon ASRAM A, the Interface, or the Flash Memory is a write operation. The target of the operation is in this case determined by the Interface based on the state of the NSEL lines discussed below. NWRA low indicates that the operation upon ASRAM B is a write operation. Note that the two NWR signals are not strobes. They are to be asserted at the time of the placement of the address and data on their respective local buses and de-

asserted upon completion of operation. They should be kept constant for the duration of a block transfer. In the UCF, the NWRA and NWRB pins are labeled NWRAOPD and NWRBOPD, respectively. Their association with physical pins of the FPGA is shown in Table 10 below.

Table 10. Write enable (output) pins of the FPGA

| NWR signal | FPGA pin | NWR signal | FPGA pin |

|------------|----------|------------|----------|

| NWRA       | 81       | NWRB       | 70       |

#### 4.4.4.6. DEVICE SELECTION PORTS

The FPGA signals to the Interface the intended target of its operation over three lines, NSELA, NSELB, and NSELV, named in UCF as NSELAOPD, NSELBOPD, and NSELVOPD. All these lines are active low and have dual functionality, depending on whether the operation is "write" or "read".

In write operations, NSEL signals serve as write strobes and, hence, must be asserted so as to allow the address to propagate to the target device prior to their own reaching of the target (via the Interface). It was found that a safe way to write to ASRAMs is to assert the relevant NSEL signal for one system clock cycle, two system clock cycles after the FPGA has placed the address and data on their respective local buses. In a block transfer, this results then in a 3-cycle transfer and in an overall throughput of 107Mbyte/s (80MHz clock). The Interface makes here use of the data byte enable signals (NDBEO<0>-<3>) to strobe only the desired memory chips (storing individual bytes).

In read operations, NSEL signals serve as chip enable signals, which in conjunction with the (ASRAM) output enable signals cause the target device to output the addressed data on the data bus. In this case, NSEL is to be asserted at the time of the placement of address on the local address bus and can be kept constantly low for the entire duration of a block transfer. The ASRAM output enable signals are generated by the Interface when the latter detects the presence of an NSEL signal in the absence of the associated NWR signal (NWR high).

There are following valid combinations of the asserted NSEL signals:

- (i) NSELA alone,

- (ii) NSELB alone,

- (iii) NSELV alone,

- (iv) NSELA and NSELV,

- (v) NSELA and NSELB, and

- (vi) NSELA and NSELB and NSELV.

(i) and (ii) are used to achieve transfer of data between the FPGA and the individual ASRAMs. (iii) is used to access the FPGA interrupt service register and the associated

flag in Interface. The combination (iv) is used (e.g., by Utility Configuration) to write data into the Flash Memory. The combination (v) allows simultaneous write by the FPGA into both ASRAMS or a transfer of data between the two ASRAMs, while the combination (vi) is intended for data transfer operations between ASRAM B and the Flash Memory (programming of the Flash Memory with a configuration file stored in ASRAM B or read-back of the content of the Flash Memory into ASRAM B). Note that an access of the Flash Memory involves asserting both NSELA and NSELV. For operations on the Flash Memory, the user is encouraged to use the default cold-boot Utility Configuration residing in bank 0 of the Flash Memory.

Note that ASRAM A shares NWRA line and the Output Enable line with the Flash Memory, which precludes transfer of data between ASRAM A and the Flash Memory. These two devices have, however, separate chip enable signals, which allows one to access any one of them individually.

The correspondence between the NSEL lines and the physical pins of the FPGA is shown in Table 11.

Table 11. Device selection pins of the FPGA

| Signal | FPGA pin | Signal | FPGA pin | Signal | FPGA pin |

|--------|----------|--------|----------|--------|----------|

| NSELA  | 93       | NSELB  | 79       | NSELV  | 54       |

#### 4.4.4.7. INTERRUPT PORTS

There are three "interrupt" lines interconnecting the FPGA and the Interface, one dedicated for transmitting interrupt signals sent from the VMEbus to the FPGA (NIRQXV), one for transmitting interrupt signals sent from the FPGA to the VMEbus (NIRQVX), and one for transmitting interrupt signals sent by the DSP to the FPGA (NIRQXD). The NIRQVX interrupt is not used in the present implementation of the Interface.

In the UCF, the NIRQXV, NIRQVX, and NIRQXD pins are labeled NIRQXVIPD, NIRQVXOPD, and NIRQXDIPD, respectively.

The association between the NIRQ signals and the physical pins of the FPGA is shown in Table 12.

| Table 12. | Interrupt pins | of the FPGA |

|-----------|----------------|-------------|

|-----------|----------------|-------------|

| IRQ    | FPGA pin | IRQ    | FPGA pin | IRQ    | FPGA pin |

|--------|----------|--------|----------|--------|----------|

| NIRQXV | 55       | NIRQVX | 78       | NIRQXD | 94       |

#### 4.4.4.8. WRITE/READ CONTROL PORTS

The Interface controls writing and reading of data into/from the FPGA registers by means of two signals NSELXV and NWRX. The mechanism is here very much the same as the one used by the FPGA to execute read and write operations.

In a write operation NWRX is low for the duration of the operation (e.g., for the duration of block transfer), while the NSELXV (active low) plays a role of the write strobe. User configuration may then utilize the leading edge of the NSELXV to register the local data LOCDA0-31 into registers identified by the local address LOCAD2-20.

In read operations, NWRX is high and NSELX is low for the duration of the operation. User configuration must then respond by placing the content of the addressed register on the local data bus and enabling the associated tri-state drivers. In this case, it is the Interface that is in control of the timing.

In UCF, the NWRX and NSELX pads are named NWRXIPD and NSELXIPD, respectively. Their association with physical pins of the FPGA is shown in Table 13 below.

Table 13. Write/read to/from FPGA control pads

| Control line | FPGA Pad # | Control line | FPGA Pad # |

|--------------|------------|--------------|------------|

| NWRX         | 52         | NSELX        | 65         |

#### 4.4.5. CONFIGURING FPGA

XLMXXV offers three ways of configuring FPGA:

- (i) via the JTAG port (see Section 4.1.3.1),

- (ii) from Flash Memory, and

- (iii) from ASRAM A.

Programming via the JTAG port is intended primarily for debugging purposes and requires dedicated equipment (software and download cable) and, therefore, is not discussed in this manual.

#### 4.4.5.1. CONFIGURATION DATA FILE

When configuring FPGA from ASRAM A or programming Flash Memory, a properly formatted configuration data file is needed. FPGA programming software allows one to generate binary configuration data as an array of 8-bit words. These 8-bit data words have to be properly mapped onto 32-bit words to be loaded into ASRAM A or ASRAM B (in the case of Flash Memory programming – see Section 4.5). The mapping is shown in Table 14 below.

Table 14. Mapping of 8-bit "raw" configuration data bytes onto 32-bit words

| Bit # in "Raw" 8-bit Word  | 0 | 1 | 2 | 3  | 4  | 5  | 6  | 7  |

|----------------------------|---|---|---|----|----|----|----|----|

| Bit # in 32-bit "XLM" Word | 2 | 3 | 4 | 10 | 18 | 19 | 20 | 26 |

Note that a "raw" byte FFh converts to a 32-bit 41C041Ch "XLM" configuration word.

Furthermore, the header part of the "raw" data file has to be skipped and only the configuration data proper converted and loaded into target ASRAM. To perform this stripping, one has to rely on the fact that the first data word to be converted is FFh (decimal 255), which means that a conversion program must skip all bytes read from a "raw" configuration file until it encounters FFh (255). Note also that second valid byte is always 0.

#### 4.4.5.2. CONFIGURING FPGA FROM FLASH MEMORY

Upon power-up, FPGA attempts to boot (configure itself) from the default, "boot" sector of Flash Memory. Whether such a boot is successful or unsuccessful, one may force FPGA to boot from a desired different sector of Flash Memory. To this end, one must:

- (i) select the desired boot sector by writing its ID (0 1), for the two sectors available) into location 800008h (see Section 4.3.1.3),

- (ii) set reset for FPGA by writing 1 into location 800004h (Section 4.3.1.2), and

- (iii) release reset for FPGA by writing 0 into location 800004h (Section 4.3.1.2).

Upon release of reset, FPGA will attempt to boot from the selected sector of Flash Memory.

#### 4.4.5.3. CONFIGURING FPGA FROM ASRAM A

To reconfigure FPGA from ASRAM A, one must:

- (i) select ASRAM A as the FPGA boot source by writing 10000h into location 800008h (Section 4.3.1.3),

- (ii) acquire control of Bus A by writing 1 into 800000h (Section 4.3.1.1)

- (iii) load the desired configuration file into ASRAM A

- (iv) release control of Bus A by writing 0 into 800000h (Section 4.3.1.1)

- (v) set reset for FPGA by writing 1 into location 800004h (Section 4.3.1.2), and

- (vi) release reset for FPGA by writing 0 into location 800004h (Section 4.3.1.2).

Upon release of reset, FPGA will attempt to boot from ASRAM A.

The above procedure has to be somewhat altered when FPGA is not yet configured. In such a case, in order to be able to acquire Bus A, one must first inhibit the bus access by FPGA and DSP by writing 1 into location 80000Ch (see Section 4.3.1.4) and then set

reset for FPGA as in (v) above. Subsequently, one would have to perform (i), (ii), (iii), (vi), and cancel inhibition of bus access by FPGA (by writing 0 into 80000Ch).

### 4.5. USING THE DSP

To use the DSP, the user must prepare an executable suitable for downloading into the DSP and boot the DSP with this executable.

#### 4.5.1. DSP ADDRESS SPACE

The TMS320C6711 DSP has a single 32-bit address space covering internal memory and registers, as well as external memories. The DSP accesses external memories through its Extended Memory Interface (EMIF), capable of handling a variety of memory types. In the XLMXXV, these external memories are the two banks of ASRAMs and the Interface, all of which present themselves to the DSP as asynchronous random access memories.

| The address space of the DSI | <b>P</b> is allocated as follows:  |

|------------------------------|------------------------------------|

| 0000 0000h                   | Internal memory of the DSP         |

| 8000 0000h                   | ASRAM A (2 Mbytes)                 |

| 9000 0000h                   | ASRAM B (2 Mbytes)                 |

| A000 0000h                   | Interface (few selected addresses) |

By default the Extended Memory Interface is set for asynchronous RAM and, hence, will work with ASRAMs and the Interface of XLMXXV. The default timing of the EMIF is, however, slow and it is advisable to set it to a much faster one. The EMIF for any particular internal device of XLMXXV can be configured by writing to the respective EMIF register. The EMIF registers have the following addresses within the DSP internal address space:

| 180 0008h | EMIF for ASRAM A     |

|-----------|----------------------|

| 180 0004h | EMIF for ASRAM B     |

| 180 0010h | EMIF for Interface   |

| 180 0000h | Global EMIF register |

#### 4.5.2. USER'S GUIDE TO HOST-PROCESSOR INTERFACE

General remarks:

- (i) The present guide applies to XLMXXVs equipped with DSPs with silicon ID C21 and not C13 used in prototype series.

- (ii) XLMXXV powers up with DSP kept in reset state. To use HPI (and the DSP in general) the reset must be removed by writing 0 to VMEBus address 800004h. Note that writing 2 to 800004h sets the DSP reset.

- (iii) By default, XLMXXV powers up with DSP boot mode set to HPI, regardless of the setting of DSP boot mode jumpers.

XLMXXV is designed to take advantage of the Host-Port Interface (HPI) of the TMS320C6711 Digital Signal Processor. Via the HPI, the XLMXXV user has access to internal registers of the DSP, as well as to the whole address space. The latter includes internal devices of XLMXXV, such as Interface, ASRAM A, and ASRAM B. Communication with HPI occurs through writing and reading to control (HPC), address (HPA), and data (HPD) registers of the DSP using part of the HPI address space set up in the Interface. The target register and the direction of transfer (read/write) are selected using 4 VMEBus address lines – A2-A4 and A10 (A0 being the least significant bit). These address lines connect (via Interface) to the HHWIL (Half-word Identification Select), HCTL[1:0] (Access Control Select), and HRW (Read/Write Select) pins of the DSP, as follows:

| DSP Pin | VME |                                                |

|---------|-----|------------------------------------------------|

| HHWIL   | A2  | HHWIL=0 selects the first (16-bit) halfword    |

| HCTL[0] | A3  | HCTL=0 selects HPC, HCTL=1 selects HPA,        |

| HCTL[1] | A4  | HCTL=2/3 select HPD with/without address auto- |

|         |     | increment                                      |

| HRW     | A10 | HRW=0/1 correspond to "Write"/"Read"           |

According to the above assignment, HPI maps onto VMEBus address space as follows:

| VMEBus Address | HPI Function                                          |

|----------------|-------------------------------------------------------|

| 600000h        | Write first half-word into HPC                        |

| 600004h        | Write second half-word into HPC                       |

| 600400h        | Read first half-word from HPC                         |

| 600404h        | Read second half-word from HPC                        |

| 600008h        | Write first half-word into HPA                        |

| 60000Ch        | Write second half-word into HPA                       |

| 600408h        | Read first half-word from HPA                         |

| 60040Ch        | Read second half-word from HPA                        |

| 600010h        | Write first half-word into HPD, with addr. autoincr.  |

| 600014h        | Write second half-word into HPD, with addr. Autoincr. |

| 600410h        | Read first half-word from HPD, with addr. autoincr.   |

| 600414h        | Read second half-word from HPD, with addr. Autoincr.  |

| 600018h        | Write first half-word into HPD, fixed address         |

| 60001Ch        | Write second half-word into HPD, fixed address        |

| 600418h        | Read first half-word from HPD, fixed address          |

| 60041Ch        | Read second half-word from HPD, fixed address         |

Note that in order to write/read to/from any address location of the DSP address space, one must first load the desired address into HPA and, for the write operation, load the data into HPD.

Reading from the HPI is somewhat tricky due to bugs in the DSP silicon. It works, however, reliably for the silicon version C21, provided after loading the address register and before reading from HPD, one writes the "fetch" bit into the control register, i.e., writing:

10h into VMEBus address 60 0000h

(Alternatively, one could read from HPD twice, the second read yielding the correct data).

In the case of reading in address autoincrement mode, only first read needs to be preceded by the "fetch" command.

#### 4.5.3. THE DSP BOOT PROCESS

On power-up, XLMXXV keeps the DSP in the state of reset. To make use of the DSP, the user must select the DSP boot mode by setting the DSP boot source jumper(s) JP35 for the desired mode and then performing the boot sequence proper for the selected mode. There are four DSP boot modes available, as labeled in silk-screen on the XLMXXV board and as shown in Table 1 in Subsection 4.1.3.2.

For XLMXXV modules with DSPs of the C21 issue (and not C13), the most convenient and, hence, advisable procedure of booting the DSP is to boot via the Host-Processor Interface (HPI). To boot via HPI, one must:

- (i) release the DSP from reset by writing 0 (or 1) to VMEBus address 80 0004h,

- (ii) load the executable into the DSP memory space via HPI, and

- (iii) release the DSP from the HPI boot mode.

Note, that (due to a hardware bug) the HPI boot is insensitive to the jumper settings, the setting being overridden by VMEBus data bits 3 and 4 that are expected to be 0. See also the warning below.

The remaining three boot modes involve ASRAM B as the boot medium and differ only in lengths of the boot data words. These modes and require:

- (i) loading of up to 1 kbyte of the executable into ASRAM B,

- (ii) setting the boot mode jumpers to the desired mode,

- (iii) granting the DSP the control over Bus B by writing 2 0000h into the VMEBus address 800000h,

- (iv) releasing DSP from reset by writing 0 (or 1) to VMEBus address 80 0004h

- (v) releasing the boot-mode grant of bus B by writing 0 to VMEBus address 800000h (see the warning below).

Warning: Step (v) of the boot sequence via ASRAM B is of great importance, as (because of a hardware bug) with Bus B allocated to DSP by the VMEBus, XLMXXV has control of the VMEBus data bus. In fact, in this state, XLMXXV outputs the boot mode jumper setting on the VMEBus data bus (bits 3 and 4). By

the same token (bug), one should not attempt step (iii) and more generally, the booting of the DSP, when there is any activity on the VMEBus data bus.

### 4.6. The INTERRUPT SYSTEM OF XLMXXV

XLMXXV features an interrupt system by which any single of its three masters, VMEBus, FPGA, and DSP can request a specific action by any one of the two remaining masters. The system includes a positive hand-shaking mechanism, by which the target device of the request may inform the requestor device of the status of the requested action.

The general strategy of the interrupt handling is as follows:

- (i) The interrupt requestor device (IRQSource) places a 14-bit interrupt code/argument (IRQID) in the dedicated interrupt request mailbox (IRQMail) register for the desired interrupt target device (IRQTarget).

- (ii) IRQSource sets an "interrupt pending" flag (IRQPending).

- (iii) IRQSource issues the service request to IRQTarget.

- (iv) IRQTarget executes the requested operation.

- (v) IRQTarget clears the relevant IRQMail register and the IRQPending flag.

- (vi) IRQSource monitors IRQPending flag for the status of the requested service.

The minimum action needed comprises of (ii) and (iii), performed always simultaneously by the XLMXXV firmware. The remaining steps are optional, with step (vi) being recommended and, perhaps, dictated by common sense.

There are two ways of issuing a service request. First is based on the polling of the IRQMail register by IRQTarget and is available in any IRQSource-IRQTarget combination. The second mechanism is based on the use of interrupt signals on dedicated interrupt lines and is not available, in the present XLMXXV firmware, for requests involving VMEBus as IRQTarget. The second mechanism appears advisable for requests involving DSP and FPGA as IRQTargets.

As IRQSource, each of the three masters of XLMXXV has available two write-only IRQMail registers and two write-only IRQPending flags, one for each of the remaining two masters.

As IRQTarget, each of the three masters of XLMXXV "sees" one read-write IRQMail register and two clear-only IRQPending flags, physically the same registers and flags accessed by the IRQSource.

#### 4.6.1. WRITING TO IRQMail REGISTERS

IRQSources access relevant IRQMail registers by writing to the Interface addresses shown in Table 15.

| IRQSource | IRQTarget | IRQMail Address for IRQSource        |

|-----------|-----------|--------------------------------------|

| VMEBus    | FPGA      | IRQMail to be set up in FPGA by User |

| VMEBus    | DSP       | 82 1048h                             |

| FPGA      | DSP       | 00 0824h                             |

| FPGA      | VME       | 00 1048h                             |

| DSP       | VME       | A000 0824h                           |

| DSP       | FPGA      | A003 1048h                           |

Table 15. IRQMail registers for various IRQSources

The desired IRQID data are to be placed on bits 2-15 of the data word written into the IRQMail register.

#### 4.6.2. ISSUING OF SERVICE REQUESTS

For a polling-based interrupting, it is sufficient for an IRQSource to write the desired IRQID data to the respective IRQMail register. For a direct interrupting, available for the DSP and the FPGA as target devices, the interrupt signal is generated automatically in some cases (VMEBus->DSP, DSP-> FPGA) upon writing into the respective IRQMail registers (see Table 16.) In the case of VMEBus requesting service by the FPGA, where no dedicated mail box is set up within the Interface, VMEBus must write (dummy write) into Interface address 62 0004h. In the case of the FPGA interrupting DSP, User must configure the FPGA to toggle one of the two interrupt pins – INT6DXOPD (pin 177), or NMIDXOPD connected directly to the INT6 and NMI (non-masked interrupt) pins of the DSP. Obviously, toggling of the desired interrupt pin can occur concurrently with writing by the FPGA to the respective IRQMail register associated with the DSP (at 00 0824h).

| IRQSource | IRQTarget | Direct Interrupt Mechanism               |

|-----------|-----------|------------------------------------------|

| VMEBus    | FPGA      | Write to 82 0004h                        |

| VMEBus    | DSP       | Write to 82 1048h generates INT4 for DSP |

| FPGA      | DSP       | Toggle INT6DXOPD/NMIDXOPD for INT6/NMI   |

| DSP       | FPGA      | Write to A003 1048h                      |

Table 16. Direct Interrupt Mechanism